## EEL 4744 DAC Reference and Output Voltages The same voltage references used for the ADC are used for the DAC Internal 1.00V Internal Vcc/1.6V (=2.0625V for Vcc=3.3V) Internal Vcc/2V External voltage at AREF pin on PORTA External voltage at AREF pin on PORTB (bits 0 & 1) The output voltages from a DAC channel, V<sub>DACn</sub>, is given by: Note the denominator is not 2<sup>12</sup> V<sub>DACn</sub> = CHnDATA OxFFF VREF

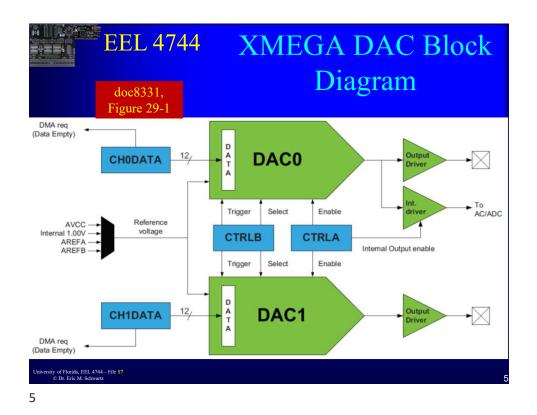

## EEL 4744 DAC – Control Register A Bit 4 – IDOEN: Internal Output Enable > Setting this bit will enable the internal DAC channel 0 output to be used by the Analog Comparator and ADC. This will then also disable the output pin for DAC Channel 0. • Bit 3 – CH1EN: Channel 1 Output Enable > Setting this bit will make channel 1 available on the output pin. • Bit 2 – CH0EN: Channel 0 Output Enable > Setting this bit will make channel 0 available on the output pin unless IDOEN is set to 1. Bit 1 – LPMODE: Low Power Mode > Setting this bit enables the DAC low-power mode. The DAC is turned off between each conversion to save current. Conversion time will be doubled when new conversions are started in this mode. • Bit 0 – ENABLE: Enable > This bit enables the entire DAC. 6 Bit 7 5 4 3 2 1 0 +0x00 IDOEN CH1EN CH0EN LPMODE ENABLE ---Read/Write R/W R/W R/W R/W R/W R R R nitial Value 0 0 0 0 0 0 0 0 File 17 DAC CTRLA ty of Florida, EEL 4744 © Dr. Eric M. Sale 6

|              |                       |                                        |              |                        |            | trol F        | Regi                | ster B                                |

|--------------|-----------------------|----------------------------------------|--------------|------------------------|------------|---------------|---------------------|---------------------------------------|

| > Thes       | e bits co             | ISEL [1:<br>ontrol whic<br>g. This tab | h DAC cl     | nannels are            | e enabled  | CHSEL<br>[30] | Group<br>Config     | Description                           |

| • Bit 1      |                       | <b>TRIG:</b> A et, an ever             |              |                        |            | 00            | Single              | Single-<br>channel op on<br>channel 0 |

| chan<br>DAC  | nel, set i            | n EVCTR<br>l 1 if its da               | L, will trig | gger a con             | version of | n<br>01       | Single1             | Single-<br>channel op on<br>channel 1 |

| • Bit 0      | – <b>CH</b> 0         | TRIG: A                                |              |                        |            | 10            | Dual                | Dual-channel<br>op                    |

| chan         | son is s<br>nel set i | et, an ever<br>n EVCTR                 | It on the c  | onngured<br>oger a con | version of | 11            |                     | Reserved                              |

| DAC          |                       | 10 if its da                           |              |                        |            |               | See doc8<br>Table 2 |                                       |

| Bit          | 7                     | 6                                      | 5            | 4                      | 3          | 2             | 1                   | 0                                     |

| -0x01        | -                     | CHSE                                   | L[1:0]       | -                      | -          | -             | CH1TRIG             | CHOTRIG                               |

| Read/Write   | R                     | R/W                                    | R/W          | R                      | R          | R             | R/W                 | R/W                                   |

| nitial Value | 0                     | 0                                      | 0            | 0                      | 0          | 0             | 0                   | 0                                     |

|              | EL 4744 - File 17     |                                        |              | DAC C                  |            |               |                     |                                       |

n III Proteine EEL 4744 DAC – Control Register C -----• Bit 4:3 – REFSEL[1:0]: Reference Selection > These bits select the reference voltage for CHSEL the DAC [3..0] Internal • Bit 0 - LEFTADJ: Left-Adjust Value INT1V 00 1.00V > If this bit is set, CH0DATA and CH1DATA 01 AVCC  $AV_{CC}$ are left-adjusted; if 0, they are right-adjusted AREF on > The 12-bit input value to the DAC is 10 AREFA PORTA contained in two 8-bit registers, referred to **AREF** on 11 AREFB PORTB as the high and low registers. - By default, the 12-bit value is distributed with the 8 LSB in the low register and 4 MSB in the high register. - This bit changes that so that the 4 LSB are in the low register and the 8 MSB are in the high register. Bit 5 4 3 2 0 +0x02 REFSEL[1:0] LEFTADJ \_ \_ \_ \_ -Read/Write R R RM RAW R/W R R R Initial Value 0 0 0 0 0 0 0 0 sity of Florida, EEL 4744 – File 17 © Dr. Eric M. Schwartz DAC CTRLC 8

University of Florida, EEL 4744 – File 17 © Dr. Eric M. Schwartz

4

|                                                                                            | EE                                                                                                                  | L 4744                                                                                                     | 4                                                                                                              | DAC                                                                                                                                  | – Sta                                                                                                                           | atus                                                                  | Regis                                                             | ter             |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|

| empt<br>> Writi<br>pend<br>> This<br>• <b>Bit 0</b> -<br>> This<br>empt<br>> Writi<br>pend | bit whe<br>y, mear<br>ng to th<br>ing con<br>bit is di<br><b>– CH(</b><br>bit whe<br>y, mear<br>ng to th<br>ing con | en set ind<br>ning that<br>ne data re<br>version d<br>irectly us<br><b>DRE:</b><br>en set ind<br>ning that | Chan<br>icates t<br>a new<br>gister<br>lata to l<br>ed for<br>Chan<br>icates t<br>a new<br>gister<br>lata to l | nel 1 D<br>hat the d<br>conversion<br>when this<br>be overw<br>DMA re<br>nel 0 D<br>hat the d<br>conversion<br>when this<br>be overw | ata Reg<br>ata regis<br>on value<br>s bit is cl<br>vritten.<br><b>quests</b><br>ata regis<br>on value<br>s bit is cl<br>vritten | gister<br>ter for<br>maybe<br>eared v<br>ister I<br>ter for<br>may be | Empty<br>channel 1<br>written<br>vill cause<br>Empty<br>channel 0 | is<br>the<br>is |

| Bit                                                                                        | 7                                                                                                                   | 6                                                                                                          | 5                                                                                                              | 4                                                                                                                                    | 3                                                                                                                               | 2                                                                     | 1                                                                 | 0               |

| +0x05                                                                                      | -                                                                                                                   | _                                                                                                          | -                                                                                                              | -                                                                                                                                    | -                                                                                                                               | -                                                                     | CH1DRE                                                            | CH0DRE          |

| Read/Write                                                                                 | R                                                                                                                   | R                                                                                                          | R                                                                                                              | R                                                                                                                                    | R                                                                                                                               | R                                                                     | R/W                                                               | R/W             |

| Initial Value                                                                              | 0                                                                                                                   | 0                                                                                                          | 0                                                                                                              | 0                                                                                                                                    | 0                                                                                                                               | 0                                                                     | 0                                                                 | 0               |

| University of Florida, EEL<br>© Dr. Eric M. Sch                                            |                                                                                                                     |                                                                                                            |                                                                                                                | DAC_STA                                                                                                                              | ATUS                                                                                                                            |                                                                       |                                                                   | 9               |

| 9                                                                                          |                                                                                                                     |                                                                                                            |                                                                                                                |                                                                                                                                      |                                                                                                                                 |                                                                       |                                                                   |                 |

9

|                                      |                                                              |                               |                                       | $\boldsymbol{\mathcal{O}}$      |                             |                            | $\sim$                   |                                      | 0,1                   |

|--------------------------------------|--------------------------------------------------------------|-------------------------------|---------------------------------------|---------------------------------|-----------------------------|----------------------------|--------------------------|--------------------------------------|-----------------------|

|                                      | Bit                                                          | 7                             | 6                                     | 5                               | 4                           | 3                          | 2                        | 1                                    | 0                     |

| Right-adjust                         | +0x18                                                        |                               |                                       |                                 | CHDA                        | TA[7:0]                    |                          |                                      |                       |

| Left-adjust                          | +0X18                                                        |                               | CHDA                                  | TA[3:0]                         |                             | -                          | -                        | -                                    | -                     |

| Right-adjust                         | Read/Write                                                   | R/W                           | R/W                                   | R/W                             | R/W                         | R/W                        | R/W                      | R/W                                  | R/W                   |

| Left-adjust                          | Read/Write                                                   | R/W                           | R/W                                   | R/W                             | R/W                         | R                          | R                        | R                                    | R                     |

| Right-adjust                         | Initial Value                                                | 0                             | 0                                     | 0                               | 0                           | 0                          | 0                        | 0                                    | 0                     |

| Left-adjust                          | Initial Value                                                | 0                             | 0                                     | 0                               | 0                           | 0                          | 0                        | 0                                    | 0                     |

|                                      | ove is fo                                                    |                               | low by                                | yte                             |                             |                            |                          | or $x = 0$ or                        |                       |

|                                      | ove is fo<br>ow is for<br>Bit                                |                               | low by                                | yte                             |                             |                            |                          |                                      |                       |

| • Bel                                | <b>DW is fo</b> r<br>Bit                                     | r the l                       | low by<br>nigh b                      | yte<br>yte                      | DA                          | C_CHxI                     | DATA, fo                 | for $x = 0$ of                       | or 1                  |

| • Belo                               | ow is fo                                                     | r the l                       | low by<br>nigh b                      | yte<br>yte<br>5                 | <b>DA</b> (                 | C_CHxI                     | DATA, fo                 | for $\mathbf{x} = 0$ of $\mathbf{x}$ | or 1                  |

|                                      | <b>DW is fo</b> r<br>Bit                                     | r the l                       | low by<br>nigh b                      | yte<br>yte<br>5                 | <b>DA</b><br>4<br>-         | C_CHxI                     | DATA, fo                 | for $\mathbf{x} = 0$ of $\mathbf{x}$ | or 1                  |

| Bele                                 | DW is for<br>Bit<br>+0x19                                    | r the l                       | low by<br>nigh b<br>-                 | yte<br>yte<br>5<br>-            | DA<br>4<br>-<br>CHDAT       | 3<br>A[11:4]               | 2<br>CHDAT               | r x = 0                              | or 1<br>0             |

| • Bel<br>Right-adjust<br>Left-adjust | DW IS for<br>Bit<br>+0x19<br>Read/Write                      | <b>r the l</b><br>7<br>-<br>R | low by<br>nigh b<br>6<br>-            | yte<br>yte<br>5<br>-<br>R       | da<br>4<br>-<br>CHDAT<br>R  | 3<br>A[11:4]<br>R/W        | 2<br>CHDAT               | 1<br>A[11:8]<br>R/W                  | or 1<br>0<br>RW       |

| Bel                                  | D <b>W is fo</b><br>Bit<br>+0x19<br>Read/Write<br>Read/Write | r the l<br>7<br>-<br>R<br>RW  | low by<br>nigh b<br>6<br>-<br>R<br>RW | yte<br>yte<br>5<br>-<br>R<br>RW | 4<br>-<br>CHDAT<br>R<br>R/W | 3<br>A[11:4]<br>R/W<br>R/W | 2<br>CHDAT<br>R/W<br>R/W | 1<br>A[11:8]<br>R/W<br>R/W           | or 1<br>0<br>RW<br>RW |

6

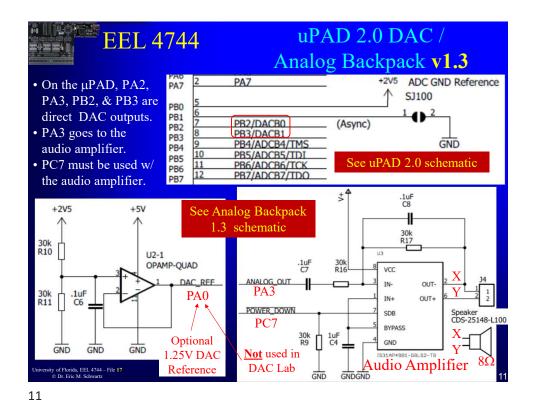

## • There are many DAC chips available

- > Ranging from parallel input to various types of serial inputs; from 8-bit to 24-bit inputs; from one channel (output) to 96 channels

- > TI makes a **16-bit**, 1-channel, 8-pin DAC, with input **from SPI**

- TI part number DAC8551

- See https://www.ti.com/lit/gpn/dac8551 or search for "TI DAC8551"

- > TI makes a **16-bit**, 2-channel, 32-pin DAC, with **parallel input**

- TI part number DAC7642

- See <u>https://www.ti.com/lit/gpn/dac7642</u> or search "TI DAC7642"

- There are many **ADC** chips available

- > TI makes a 24-bit, 18-pin, 4-channel [Sigma-Delta] ADC with SPI output

- TI part number ADS1211P

- See <u>https://www.ti.com/lit/gpn/ads1211</u> or search for "TI ADS1211P"

- > From TI: A 16-bit, 36-pin, 1-channel [Successive Approx] ADC with parallel output

- TI part number ADS8411

- See <u>https://www.ti.com/lit/gpn/ADS8411</u> or search for "TI ADS8411"

University of Florida, EEL 4744 – File 17 © Dr. Eric M. Schwartz

## 12

13

University of Florida, EEL 4744 – File 17 © Dr. Eric M. Schwartz

7